EP1C6Q240C8N IC FPGA 185 уводаў/вывадаў 240QFP

Параметр прадукту

Апісанне

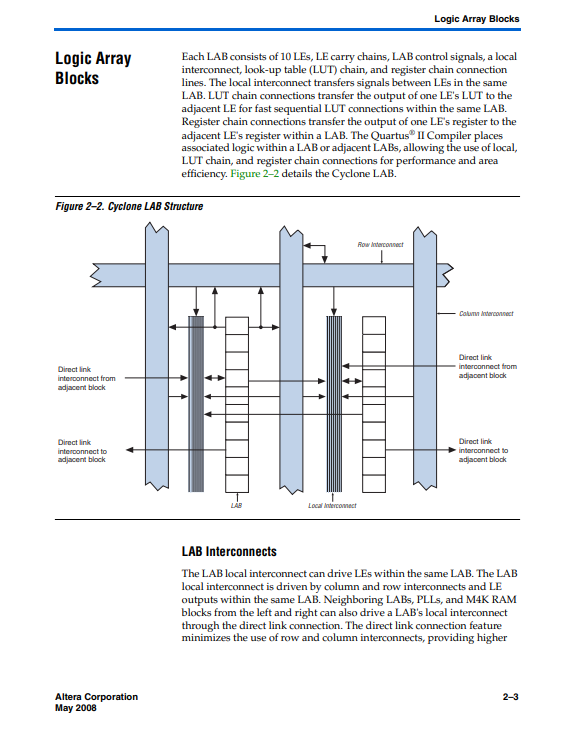

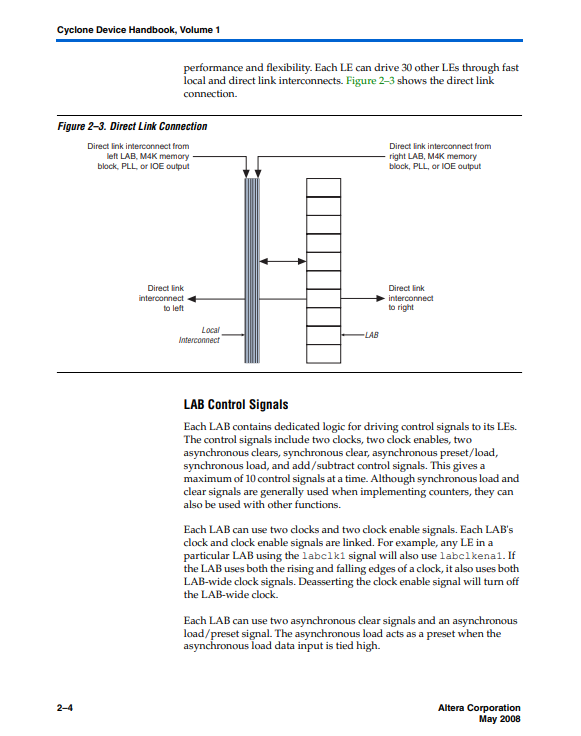

Прылады Cyclone® утрымліваюць двухмерную архітэктуру на аснове радкоў і слупкоў для рэалізацыі індывідуальнай логікі.Межзлучэнні слупкоў і радкоў з рознай хуткасцю забяспечваюць злучэнне сігналаў паміж LAB і ўбудаванымі блокамі памяці.Лагічны масіў складаецца з LAB, па 10 LE у кожнай LAB.LE - гэта невялікая лагічная адзінка, якая забяспечвае эфектыўную рэалізацыю лагічных функцый карыстальніка.ЛАБ згрупаваны ў радкі і слупкі на ўсёй прыладзе.Прылады Cyclone вар'іруюцца ад 2910 да 20060 LE.Блокі аператыўнай памяці M4K - гэта сапраўдныя двухпортавыя блокі памяці з 4K біт памяці плюс парытэт (4608 біт).Гэтыя блокі забяспечваюць выдзеленую сапраўдную двухпортавую, простую двухпортавую або аднапортавую памяць шырынёй да 36 біт і частатой да 250 МГц.Гэтыя блокі згрупаваны ў слупкі на прыладзе паміж пэўнымі LAB.Прылады Cyclone прапануюць ад 60 да 288 Кбіт убудаванай аператыўнай памяці.Кожны кантакт уводу-вываду прылады Cyclone сілкуецца элементам уводу-вываду (IOE), размешчаным на канцах радкоў і слупкоў LAB па перыферыі прылады.Кантакты ўводу/вываду падтрымліваюць розныя аднакантовыя і дыферэнцыяльныя стандарты ўводу/вываду, такія як 66- і 33-МГц, 64- і 32-бітны стандарт PCI і стандарт уводу/вываду LVDS з хуткасцю да 640 Мбіт/с.Кожны IOE змяшчае двухнакіраваны буфер уводу/вываду і тры рэгістры для рэгістрацыі сігналаў уводу, вываду і дазволу вываду.Штыфты падвойнага прызначэння DQS, DQ і DM разам з ланцужкамі затрымкі (выкарыстоўваюцца для выраўноўвання фазы сігналаў DDR) забяспечваюць падтрымку інтэрфейсу з прыладамі вонкавай памяці, такімі як прылады DDR SDRAM і FCRAM з хуткасцю да 133 МГц (266 Мбіт/с).Прылады Cyclone забяспечваюць глабальную тактавую сетку і да двух PLL.Глабальная тактавая сетка складаецца з васьмі глабальных тактавых ліній, якія праходзяць праз усю прыладу.Глабальная сетка тактавага сігналу можа забяспечваць тактавы сігнал для ўсіх рэсурсаў прылады, такіх як IOE, LE і блокі памяці.Глабальныя тактавыя лініі таксама можна выкарыстоўваць для сігналаў кіравання.Цыклонныя сістэмы ФАПЧ забяспечваюць тактаванне агульнага прызначэння з памнажэннем тактавай частоты і зрухам па фазе, а таксама знешнія выхады для падтрымкі высакахуткаснага дыферэнцыяльнага ўводу-вываду.

| Тэхнічныя характарыстыкі: | |

| Атрыбут | Каштоўнасць |

| Катэгорыя | Інтэгральныя схемы (ІС) |

| Убудаваны - FPGA (праграмуемая палявым матрыцай) | |

| Вытворца | Intel |

| серыял | Цыклон® |

| Пакет | паднос |

| Частка Статус | Устарэлы |

| Колькасць LAB/CLB | 598 |

| Колькасць лагічных элементаў/ячэек | 5980 |

| Агульная колькасць біт аператыўнай памяці | 92160 |

| Колькасць уводаў-вывадаў | 185 |

| Напружанне - сілкаванне | 1,425 В ~ 1,575 В |

| Тып мацавання | Павярхоўны мантаж |

| Працоўная тэмпература | 0°C ~ 85°C (TJ) |

| Пакет / Чахол | 240-BFQFP |

| Пакет прылады пастаўшчыка | 240-PQFP (32x32) |

| Базавы нумар прадукту | EP1C6 |

РоднасныяПРАДУКТЫ

-

тэл

-

Электронная пошта

-

скайп

-

WhatsApp

WhatsApp